Product Details

Advanced Utilization of Formal Methods in Automatic Test Pattern Generation for Industrial Designs (Berichte aus der Infor…

Free Shipping+Easy returns

Product Details

High Quality Test Pattern Generation and Boolean Satisfiability

Free Shipping+Easy returns

Product Details

Automatic test pattern generation Third Edition

Free Shipping+Easy returns

Product Details

Test Pattern Generation using Boolean Proof Engines

Free Shipping+Easy returns

Product Details

Automatic Control, Mechatronics and Industrial Engineering: Proceedings of the International Conference on Automatic Contr…

Free Shipping+Easy returns

Product Details

CNC Machining Certification Exam Guide: Setup, Operation, and Programming

Free Shipping+Easy returns

Product Details

Professional Upgraded DDS Signal Generator Counter, Seesii 60MHz LCD Display High Precision 200MSa/s Dual-Channel Arbitray…

Free Shipping+Easy returns

Product Details

Logic Synthesis for Genetic Diseases: Modeling Disease Behavior Using Boolean Networks

Free Shipping+Easy returns

Product Details

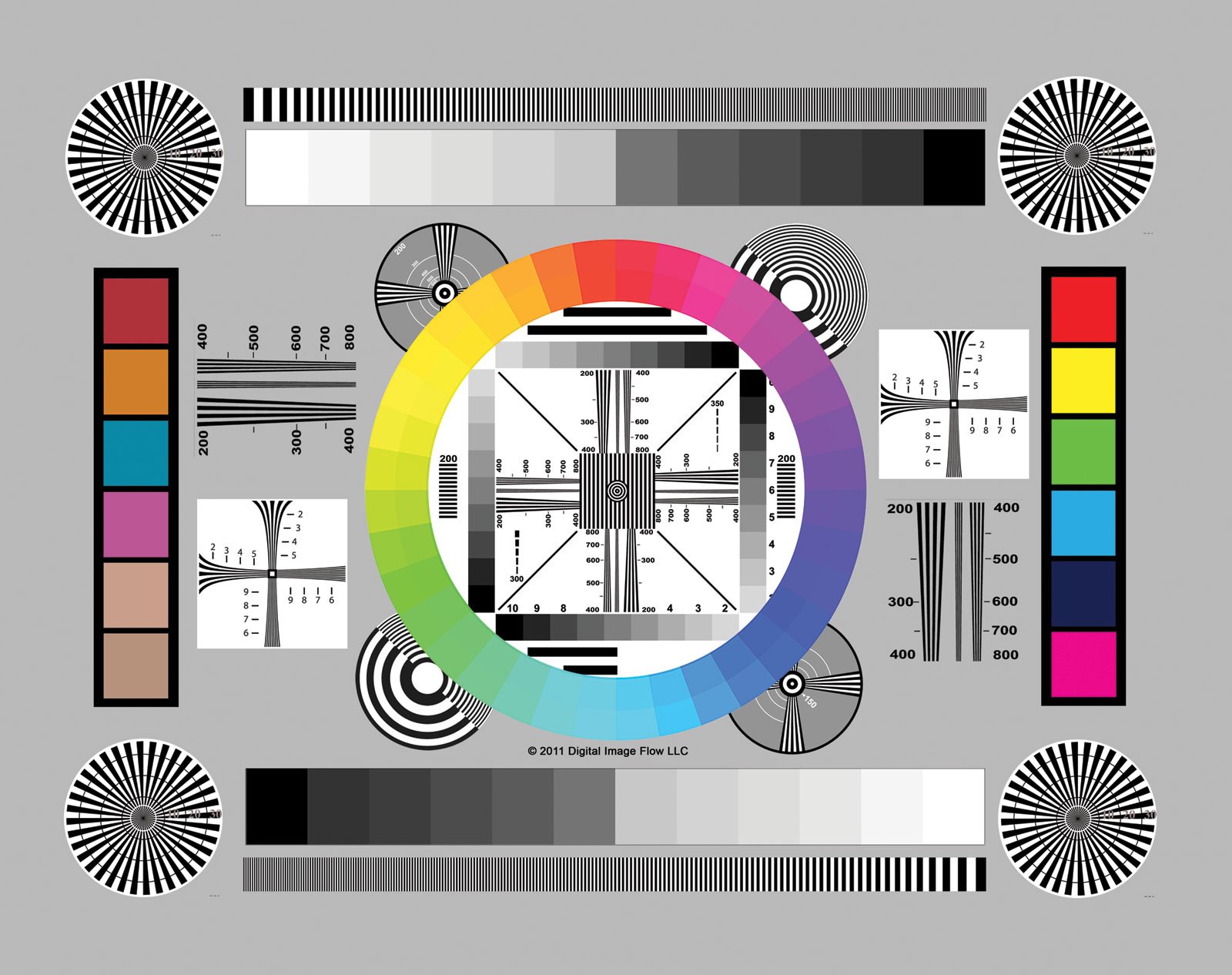

DGK Color Tools High Resolution 8.5×11" Chrome SD Professional Lens Test Chart, 3-Pack

Free Shipping+Easy returns

Product Details

Modeling Digital Switching Circuits with Linear Algebra (Synthesis Lectures on Digital Circuits and Systems)

Free Shipping+Easy returns

Product Details

Face Detection and Recognition: Theory and Practice

Free Shipping+Easy returns

Product Details

Testing for Small-Delay Defects in Nanoscale CMOS Integrated Circuits (Devices, Circuits, and Systems)

Free Shipping+Easy returns

Robustness and Usability in Modern Design Flows (Hardcover)

Dedication. List of Figures. List of Tables. Preface. 1. Introduction. 2. Preliminaries. 2.1 Boolean Reasoning. 2.2 Circuits. 2.3 Formal Verification. 2.4 Automatic Test Pattern Generation. 3. Algorithms and Data Structures. 3.1 Combining SAT and BDD Provers. 3.2 Summary and Future Work. 4. Synthesis. 4.1 Synthesis of SystemC. 4.2 Synthesis for Testability. 4.3 Summary and Future Work. 5. Property Generation. 5.1 Detecting Gaps in Testbenches. 5.2 Design Understanding. 5.3 Summary and Future Work. 6. Diagnosis. 6.1 Comparing SAT-based and Simulation-based Approaches. 6.2 Generating Counterexamples for Diagnosis. 6.3 Debugging Properties. 6.4 Summary and Future Work. 7. Summary and Conclusions. References. Index of Symbols. Index. • Author: G\\u0026ouml;rschwin Fey,Rolf Drechsler • ISBN:9781402065354 • Format:Hardcover • Publication Date:2008-01-08

Formal Methods for Hardware Verification : 6th International School on Formal Methods for the Design of Computer, Communication, and Software Systems, Sfm 2006, Bertinoro, Italy, May 22-27, 2006, Advances Lectures (Paperback)

This book presents 8 papers accompanying the lectures of leading researchers given at the 6th edition of the International School on Formal Methods for the Design of Computer, Communication and Software Systems (SFM 2006). SFM 2006 was devoted to formal techniques for hardware verification and covers several aspects of the hardware design process, including hardware design languages and simulation, property specification formalisms, automatic test pattern generation, symbolic trajectory evaluation, and more. • ISBN:9783540343042 • Format:Paperback • Publication Date:2006-07-01

High Quality Test Pattern Generation and Boolean Satisfiability (Paperback)

This book provides an overview of automatic test pattern generation (ATPG) and introduces novel techniques to complement classical ATPG, based on Boolean Satisfiability (SAT). A fast and highly fault efficient SAT-based ATPG framework is presented which is also able to generate high-quality delay tests such as robust path delay tests, as well as tests with long propagation paths to detect small delay defects. The aim of the techniques and methodologies presented in this book is to improve SAT-based ATPG, in order to make it applicable in industrial practice. Readers will learn to improve the performance and robustness of the overall test generation process, so that the ATPG algorithm reliably will generate test patterns for most targeted faults in acceptable run time to meet the high fault coverage demands of industry. The techniques and improvements presented in this book provide the following advantages: Provides a comprehensive introduction to test generation and Boolean Satisfiability (SAT); Describes a highly fault efficient SAT-based ATPG framework; Introduces circuit-oriented SAT solving techniques, which make use of structural information and are able to accelerate the search process significantly; Provides SAT formulations for the prevalent delay faults models, in addition to the classical stuck-at fault model; Includes an industrial perspective on the sta

te of the-art in the testing, along with SAT; two topics typically distinguished from each other. • Author: Stephan Eggersgl\\u0026uuml;\\u0026szlig;,Rolf Drechsler • ISBN:9781489988478 • Format:Paperback • Publication Date:2014-10-20

The Springer International Engineering and Computer Science: Assessing Fault Model and Test Quality (Paperback)

For many years, the dominant fault model in automatic test pattern generation (ATPG) for digital integrated circuits has been the stuck-at fault model. The static nature of stuck at fault testing when compared to the extremely dynamic nature of integrated circuit (IC) technology has caused many to question whether or not stuck-at fault based testing is still viable. Attempts at answering this question have not been wholly satisfying due to a lack of true quantification, statistical significance, and/or high computational expense. In this monograph we introduce a methodology to address the question in a manner which circumvents the drawbacks of previous approaches. The method is based on symbolic Boolean functional analyses using Ordered Binary Decision Diagrams (OBDDs). OBDDs have been conjectured to be an attractive representation form for Boolean functions, although cases exist for which their complexity is guaranteed to grow exponentially with input cardinality. Classes of Boolean functions which exploit the efficiencies inherent in OBDDs to a very great extent are examined in Chapter 7. Exact equations giving their OBDD sizes are derived, whereas until very recently only size bounds have been available. These size equations suggest that straight forward applications of OBDDs to design and test related problems may not prove as fruitful as was once thought. • Author: Kenneth M Butler,M Ray Mercer • ISBN:9781461366027 • Format:Paperback • Publication Date:2012-09-27

Internet Service Providers, Global or Local? (Paperback)

This book examines the role of Internet service providers (ISPs) in cities of middle and high-income countries that are not part of the English language dominance often attributed to the Internet use. It analyses structural, dynamic factors from the socio- economic, technological, and policy domains that affect the provision of Internet services. It also provides the most detailed examination yet produced of individual ISPs and the environment in which they operate in middle and high-income countries. This research also examines the contribution of ISPs towards the creation of information societies in Latin America and Western Europe. This research uses a theoretical framework based on the tension between localisation and globalisation processes that affect the activities of agents of change, the ISPs, and the competition between local and the global players in providing Internet services. A central issue of this research is whether an appropriate set of technological, socio-economic and political components may be established at city level to increase the value and capabilities for using Internet technologies. Internet Service Providers, Global or Local? (Paperback)

Efficient Test Data Compression and Fault Analysis in Vlsi Circuits (Paperback)

In higher order SOC (System On Chip) circuit, designs have led to drastic increase in test data volume. Larger test data size demands not only higher memory requirements, but also an increase in testing time. Test data compression addresses this problem by reducing the test data volume without affecting the overall system performance. In this, testable input data (test data) is generated by using Automatic test pattern generation (ATPG) then it is compressed and compressed data stored to memory. To test the particular circuit that time we will decompress the stored memory test data and then decompressed test data given to the Design Under Test (DUT). Finally DUT fault is tested and identified. It proposes a test compression technique using efficient dictionary selection and bitmask method to significantly reduce the testing time and memory requirements. This algorithm giving a best possible test compression of 92% when compared with other compression methods. • Author: Sivaganesan Subramaniam • ISBN:9786138834304 • Format:Paperback • Publication Date:2019-05-31

K-best Decoders for 5g+ Wireless Communication (Hardcover)

This book discusses new, efficient and hardware realizable algorithms that can attain the performance of beyond 5G wireless communication. The authors explain topics gradually, stepping from basic MIMO detection to optimized schemes for both hard and soft domain MIMO detection and also to the feasible VLSI implementation, scalable to any MIMO configuration (including massive MIMO, used in satellite/space communication). The techniques described in this book enable readers to implement real designs, with reduced computational complexity and improved performance. • Author: Mehnaz Rahman,Gwan S Choi • ISBN:9783319428086 • Format:Hardcover • Publication Date:2016-09-07